SIC MOSFET

# Gate-Source 전압의 Surge 억제 방법

MOSFET 이나 IGBT 등의 Power 반도체는 여러 전원 Application 이나 전력 Line 의 Switching 소자로써 사용되지만, 최근 채용이 가속되고 있는 SiC MOSFET 는 Switching 시 전압과 전류의 변화가 Device 자체의 Package Inductance 와 주변 회로의 배선 Inductance 의 영향을 무시할 수 없을 정도의 고속 동작을 하고 있습니다. 특히 Gate-Source 간 전압은 Device 자체의 전압과 전류가 변화할 때 예기치 않은 순 or 역방향 Surge 가 발생하고 있어 그 대책에 대해서 여러 검토가 진행되고 있습니다. 따라서 본 Application Note 에서는 MOSFET 의 Gate-Source 간에 발생하는 Surge 의 발생 원인을 명확히 하면서 최적의 대책방법을 제시하는 것을 목적으로 하고 있습니다.

#### Gate-Source 전압에 발생하는 Surge

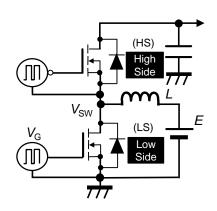

Application Note「Bridge 구성에서 Gate-Source 전압의 작용 1 \*1 으로, Bridge 구성에 의한 Switching Device 의 Turn-on 혹은 Turn-off 시에 발생하는 Gate-Source 전압의 Surge 에 대해 자세히 설명하였습니다만, Figure 1.에 나타내고 있는 동기방식 Switching 측(LS)만이 아닌 동기측(HS)에도 Switching 측의 전압과 전류의 변화에 따라서 Surge 가 있습니다.

Figure 1. 동기방식 Boost 회로

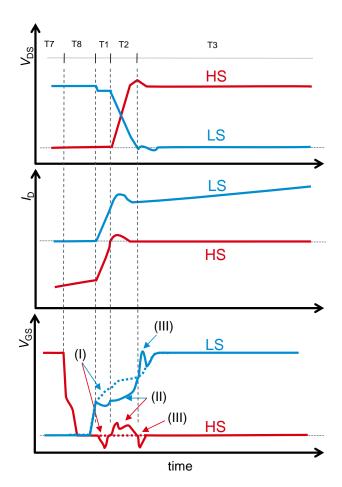

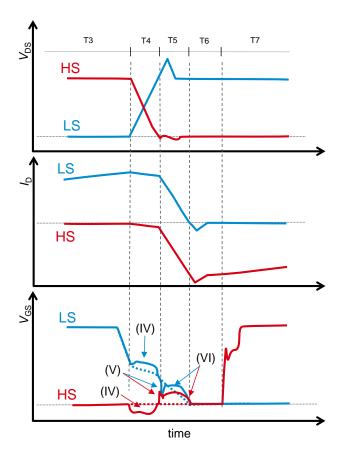

Figure 2.에서 LS Turn-on 시에 Figure 3.의 LS Turn-off 시의 Gate-Source 전압의 동작에 대해 나타냅니다. 가로축은 시간을 표시하였으며 시간 영역 Tk(k=1~8)의 정의는 각각 하기와 같습니다.

T1:LS 가 ON 하여 MOSFET 의 전류가 변화하는 구간 T2:LS 가 ON 하여 MOSFET 의 전압이 변화하는 구간 T3:LS 가 ON 하고있는 구간

T4:LS 가 OFF 하여 MOSFET 의 전압이 변화하는 구간 T5:LS 가 OFF 하여 MOSFET 의 전류가 변화하는 구간 T4-T6:HS 가 ON 할 때까지의 Dead Time 구간

T7:HS 가 ON 하고있는 구간 (동기정류 구간) T8:HS가OFF하여 LS가ON할때까지의 Dead time 구간

Figure 2. Gate-Source 전압의 동작(Turn-on 시)

Figure 3. Gate-Source 전압의 동작(Turn-off 시)

Graph 안에 표시되어 있는 현상 (I)~(IV)은 하기의 원인에 의해 발생하고 있습니다.

현상 (I), (VI) : Drain 전류의 변화(d/b/d/t)

현상 (II), (IV) : Drain-Source 전압의 변화(d 1/os/dt)

현상 (Ⅲ), (V) : Drain-Source 전압의 변화 종료

#### Surge 억제 회로

앞에서 설명한 것처럼 Gate-Source 전압(1/Gs)의 순방향 Surge 는 Switching 측과 Switching 하지 않는 양측에 발생합니다만, 특히 문제되는 것은 Turn-on 시의 Switching 하지 않는 소자(Figure 2.현상(Ⅱ))입니다.

이유는 Switching 측이 벌써 Turn-on 되어있는 상태로비 Switching 측의 순방향 Surge 전압이 MOSFET 의 Gate 문턱전압(VGS(th))을 넘는 경우, 동시 On 이 발생하여 관통전류가 흐르기 때문입니다. 단, SiC MOSFET 의 Trans-Conductance 는 Si계통의 MOSFET 에 비해 한자리수 이상 작으므로 바로 큰 관통 전류는 흐르지 않습니다. 그로 인해 관통전류가 흐르더라도 냉각능력이 충분하여 MOSFET 의  $T_{i(max)}$ 를 안 넘으면 기본적으로 문제없습니다. 그렇다 하여도 System 전체의 효율저하와 직결되므로 결코 바람직한 상태가 아니기 때문에 문턱전압 VGS(th)을 넘지 않도록 억제 회로를 추가하는 것이 요구됩니다.

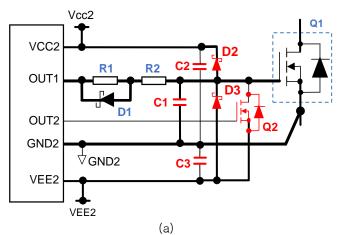

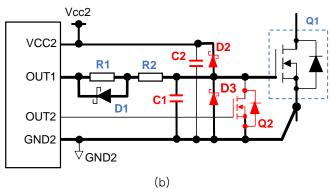

여기서, Figure 4.에 그 억제 회로를 나타냅니다.

이 도면에서는 MOSFET 의 일반적인 구동 회로에 Surge 억제용 회로를 추가하여 Table 1.에 그 기능을 나타냅니다. 또한, VCC2 는 On 용 구동전원, VEE2 는 Off 용 전원, OUT1은 MOSFET의 On/Off신호, OUT2는 Mirror Clamp용 제어신호, GND2 는 구동회로의 GND 를 나타내며, Off 용 구동 전원을 사용하는 경우를 Figure 4. (a)에, 사용하지 않는 경우를 (b)로 나타내었습니다.

Figure 4. 정방향 전압 Surge 억제 회로

(a) Minus Bias(VEE2 있음) 구동, (b) 0V Bias(VEE2 없음) 구동

Table 1. Surge 억제 회로의 기능 일람

| 효과       | Symbol | Details                       |

|----------|--------|-------------------------------|

| 순방향      | D2     | Switching 측 Turn-on 시 순방향     |

| Surge 억제 | (C2)   | Surge 전압 억제(C2는 Bypass)       |

| 역방향      | D3     | Switching / 비 Switching 측 역방향 |

| Surge 억제 | (C3)   | Surge 억제(C3는 Bypass)          |

| 순/역방향    | Q2     | 비 Switching 측 순/역방향           |

| Surge 억제 |        | Surge 억제                      |

| 오동작 억제   | C1     | 비 Switching 측 순방향 Surge 억제    |

통상 D2, D3 은 수십 ns 의 Pulse 를 흡수하여 가능한 낮은 전압으로 Clamping 할 필요가 있기 때문에 Schottky Barrier Diode(SBD)를 사용합니다. 또한 SOD-323FL 같은 밑면 전극 Type 의 Low-Impedance Package 품을 선정하는 것이 효과적입니다.

### 순방향 Surge 대책

Figure 2.에 나타낸 Turn-on 시의 비 Switching 측 V<sub>GS</sub>의 순방향 현상(II)을 억제하기 위해서는 Table 1.에 표시된 Q2 혹은 C1 이 효과적입니다.

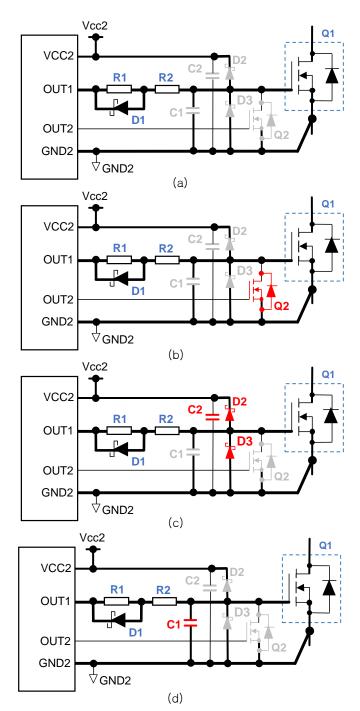

Figure 5. Surge 억제 회로의 검증 회로

(a) 억제 회로 없음, (b) Mirror Clamp 용 MOSFET 만

(c) Clamp 용 SBD 만, (d) 오동작 억제용 콘덴서만

당사 SiC MOSFET(SCT3040KR)을 사용하여 억제 회로의 효과를 검증하기 위해서 억제 회로를 개별로 실장하여 그 파형을 관측하였습니다. Figure 6.에 사용한 Device 의 외관과 개략의 사양을 나타냅니다.

| $V_{DSS}$           | 1200 V |  |

|---------------------|--------|--|

| R <sub>DS(on)</sub> | 40 mΩ  |  |

| $I_{D}$             | 55 A   |  |

| P <sub>D</sub>      | 262 W  |  |

Figure 6. SCT3040KR(4L) 외관과 개략 사양

Figure 5.와 같이 억제 회로의 조합은,

(a) 억제 회로 없음, (b) Mirror Clamp 용 MOSFET(Q2)만, (c) Clamp 용 SBD(D2,D3,C2)만, (d) 오동작 억제용 콘덴서 (C1)만의 4 가지 조합으로 Figure 7.에 나타낸 Double Pulse 실험으로 Vas 의 Surge 전압을 확인하였습니다.

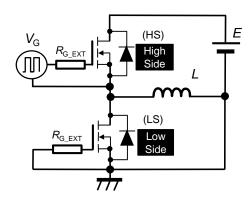

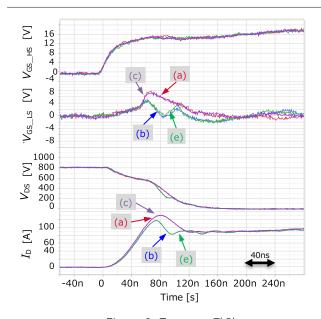

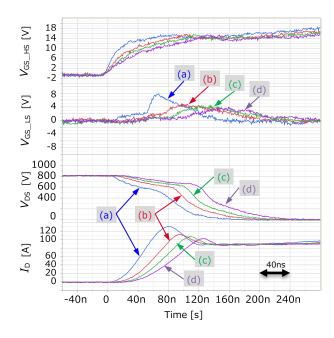

*E*: 800V, *L*: 250uH, *R*<sub>G\_EXT</sub>: 10Ω Figure 7. Double Pulse 실험 회로

Figure 8.은 Turn-on 시의 파형으로 위쪽부터 Switching 측 Gate-Source 전압(V<sub>GS\_HS</sub>), 비 Switching 측 Gate-Source 전압(V<sub>GS\_LS</sub>), Drain-Source 전압(V<sub>SS</sub>), Drain 전류(6)를 나타내었으며 억제 회로 (a), (b), (c)와 Figure 4.(b) 억제 회로 (e)의 4 가지 파형을 겹쳐서 표시하였습니다.

Figure 8.에 의해 명확히 알 수 있듯이, 대책 회로가 없는 (a)와 Clamp 용 SBD 만의 (c)로는 순방향 Surge 를 억누르지 못하고 VGS\_LS 가 튀어올라 VGS(th)를 크게 초과하고 있어 대책 회로가 있을 때의 6 보다 커진 것을 알 수 있습니다. 즉, 비 Switching 측의 MOSFET (본 회로의 LS 측)가 오동작하게 되었습니다. 이 동작을 방지하기 위해 대책 회로 (b)가 반드시 필요합니다.

(b)를 대비하기 위해서는 Mirror Clamp 용 MOSFET 를 구동하기 위한 제어 신호가 필요합니다. 그 신호는, VGS 전압을 모니터 하면서 동작 Timing 을 찾아낼 필요가 있어, 일반적으로는 구동 IC 에 갖춰져 있는 경우가 많으므로 제어기능이 없는 구동 IC 를 선정한 경우에는 이대책 회로를 선택할 수 없습니다.

Figure 8. Turn-on 파형 (a) 억제 회로 없음, (b) Mirror Clamp 용 MOSFET 만,

(c) Clamp 용 SBD 만, (e) Mirror Clamp 용 MOSFET+Clamp 용 SBD

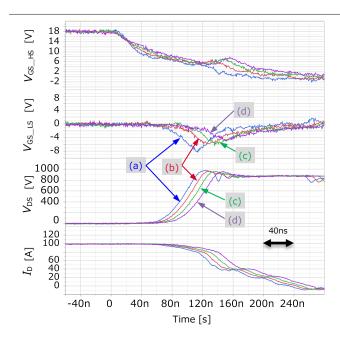

여기서, Figure 5. (d)에 나타낸 것처럼 MOSFET 의 Gate-Source 간에 오동작 억제 콘덴서를 접속시키는, Surge 대책 회로가 있습니다. Figure 9.에 오동작 억제 콘덴서를 접속했을 시의 Turn-on 파형을 나타냅니다. 억제 회로가 없는 (a)와 비교해 오동작 억제 콘덴서를 접속한 (b), (c), (d)에 대해서, VGS\_LS의 튀어 오름이 작아져 &의 Turn-on Surge 가 작아졌음을 알 수 있습니다.

Figure 9. 오동작 억제 콘덴서를 사용한 Turn-on 파형

(a) 억제 회로 없음, (b) 2.2nF, (c) 3.3nF, (d) 4.7nF

단, 16의 파형에서도 알 수 있듯이 오동작 억제 콘덴서를

접속하면 Turn-on 동작이 늦어져 Switching 손실을

증가합니다. 그러므로 필요한 최소한의 값을 선택할

필요가 있습니다. 본 평가에서는 (b) 2.2nF 로 충분한 결과가 되었습니다.

#### 역전압 Surge 대책

Figure 3.에 나타낸 Turn-off 시의 비 Switching 측  $V_{GS}$ 의 역방향 Surge 가 있는 현상 (IV)를 억제하기 위해서는 Table 1.에 나타낸 Q2 혹은 D3 이 효과적입니다.

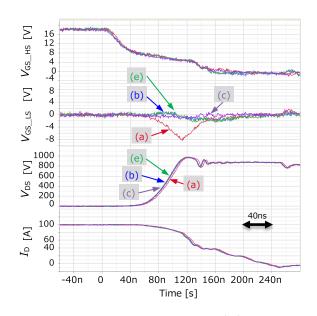

Figure 10. Turn-off 파형 (a) 제어 회로, (b) Mirror Clamp 용 MOSFET 만,

Figure 10.에 Turn-off 시의 파형을 나타냅니다. Figure 8.과 동일하게 위쪽부터 V<sub>GS\_HS</sub>, V<sub>GS\_LS</sub>, V<sub>DS</sub>, b를나타내며, 억제 회로 (a), (b), (c)와 Figure 4.(b)의 억제 회로 (e)의 4 가지 파형을 겹쳐서 표시하고 있습니다. 어느 억제 회로든 역방향 Surge 제거가 가능함을 알 수 있습니다.

(c) Clamp 용 SBD 만, (e) Mirror Clamp 용 MOSFET+Clamp 용 SBD

또한, Figure 11.에 오동작 억제 콘덴서를 접속한 경우의 Turn-off 파형을 나타냅니다. 오동작 억제 콘덴서로는 역방향 Surge 를 제거 할 수 없으므로 억제 회로 (b)를 선택할 수 없는 경우에는 (c)와 (d)를 병행 사용하여 시스템 전체의 효율을 최적화시킬 필요가 있습니다.

Figure 11. 오동작 억제 콘덴서를 사용한 Turn-off 파형 (a) 억제 회로 없음, (b) 2.2nF, (c) 3.3nF, (d) 4.7nF

## 억제 회로의 Layout 에 관한 주의점

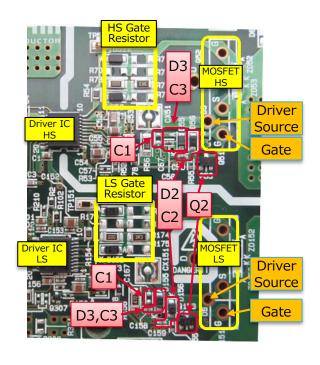

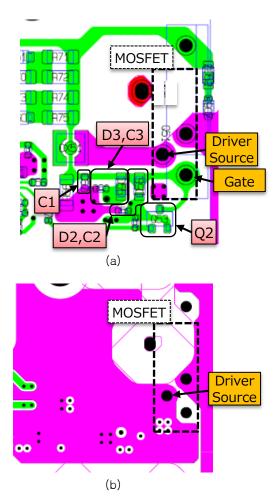

Figure 12.에 억제 회로의 Layout 예시를 나타냅니다.

Figure 12. 억제 회로 Layout 사례

이 기판에서는 Bridge 로 구성된 MOSFET 가 상/하로 배치되어 있으며 Gate 단자와 Driver Source 단자가 각 MOSFET의 하측에 배치되어 있습니다. 그리고, Ves Surge 전압의 억제 회로는 각 Gate 단자의 가장 가까운 곳에 배치되어 있어 최단 거리로 접속되어 있습니다

Figure 13.에 억제 회로의 Pattern Layout 을 나타냅니다.

복수의 억제 회로를 고려하는 경우에는, 우선 Mirror Clamp 용 MOSFET (Q2)의 실장 위치를 최우선적으로 결정해야 합니다. 그 다음 역방향 Surge Clamp 용 SBD(D3)와 Bypass 콘덴서(C3)를 배치하고, 순방향 Surge Clamp 용 SBD(D2)와 Bypass 콘덴서(C2), 오동작 억제 콘덴서(C1)의 순서로 배치를 결정해야 합니다. 그 이유는 특히 Mirror Clamp 용 MOSFET 는 수 cm 떨어뜨린 것 만으로도 그 배선의 Inductance 의 영향에 의해 억제효과가 크게 감쇠해 버리기 때문입니다.

또한, 억제 회로의 Feedback 선(Driver Source 단자로의 Feedback 선), 억제 회로의 배선에 의한 Loop 를 최소화해야 합니다. 그 이유는 SiC MOSFET의 고속 Switching 에 의한 6로 발생하는 6년 에 의해 EMC Noise 가 커지므로이 배선 Loop 가 6에 의한 EMC Noise 를 붙잡지 못하게하기 위함입니다.

본 평가 기판은 4 층 구조로, Layer2 층 전체를 GND 배선으로 사용하고 있어 억제 회로 바로 아래로 배선이 가능하므로 Loop 면적의 최소화가 가능합니다.

Figure 13. 억제 회로의 Pattern Layout (a) Layer 1, (b) Layer 2

또한, Clamp 용 SBD 에 병행 설계되어 있는 Bypass 콘덴서는 구동 전원으로부터의 Impedance 가 충분히 작다면 필요 없지만, 일반적인 공급원이 떨어져 있는 경우가 많아 SBD 의 근처에 Bypass 콘덴서를 배치하여 SBD 를 Low-Impedance 로 동작시킬 필요가 있습니다. 아울러 콘덴서의 선정에 있어서, Impedance 특성을 충분히 고려하여 수십 MHz 정도의 공진점을 갖는 콘덴서(0.1uF, 1.0 x 0.5mm Size)를 추천합니다.

이상과 같이 Bridge 구성에 의한 SiC MOSFET 의 Gate 신호는 MOSFET 간 서로 관련되어 동작하며, Gate-Source 간 전압에 예기치 않은 Surge 전압을 발생시킵니다. 그를 억제하기 위해서는 기판의 Pattern Layout 및 주변부품의 선정/조합 등의 여러가지 대책을 필요로 합니다. 본 자료에서 제시한 방법을 활용하여 각각의 상황에 맞춘 최적의 대책을 선택할 수 있기를 기대합니다.

이상

#### 참고자료:

\*1 「Bridge 구성에서 Gate-Source 전압의 작용」 Application Note (No. 63AN110K Rev.001) 로옴 주식회사, 2020 년 9월

#### Notes

- 1) The information contained herein is subject to change without notice.

- Before you use our Products, please contact our sales representative and verify the latest specifications:

- 3) Although ROHM is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. ROHM shall have no responsibility for any damages arising out of the use of our Poducts beyond the rating specified by ROHM.

- 4) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 5) The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. ROHM does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by ROHM or any other parties. ROHM shall have no responsibility whatsoever for any dispute arising out of the use of such technical information.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a ROHM representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) ROHM shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) ROHM has used reasonable care to ensure the accuracy of the information contained in this document. However, ROHM does not warrants that such information is error-free, and ROHM shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. ROHM shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of ROHM.

Thank you for your accessing to ROHM product informations. More detail product informations and catalogs are available, please contact us.

# ROHM Customer Support System

http://www.rohm.com/contact/